Porting OpenBSD to RISC-V ISA

A Project Report

Presented to

The Faculty of the Department of Computer Engineering San José State University

In Partial Fulfillment of the Requirements for the Degree Master of Science in Computer Engineering Master of Science in Software Engineering

by Brian Bamsch, Wenyan He, Mengshi Li, Shivam Waghela May 2020

Copyright © 2020

Brian Bamsch, Wenyan He, Mengshi Li, Shivam Waghela

ALL RIGHTS RESERVED

# APPROVED

M. Larkin

Michael Larkin, Project Advisor

David Bruck, Director, MS Computer Engineering

Dan Harkey, Director, MS Software Engineering

Xiao Su, Department Chair

#### ABSTRACT

# PORTING OPENBSD TO RISC-V ISA

by Brian Bamsch, Wenyan He, Mengshi Li, Shivam Waghela

The RISC-V ISA shows significant promise as an upcoming, flexible ISA for general purpose computing. However, adoption of RISC-V is largely hindered by lack of software support, particularly among popular operating systems. Only a few operating systems, including Linux and FreeBSD, have been updated to support RISC-V. Many other operating systems, including OpenBSD, do not yet run on RISC-V hardware. This project makes the first step towards a port of OpenBSD by introducing support for the RISC-V ISA within the OpenBSD kernel. As part of this effort, a deep-dive is performed into the machine-dependent aspects of bootstrap, memory, trap, process, and device subsystems of the OpenBSD kernel. The ported OpenBSD kernel has implemented early bootstrap logic in assembly, adapted PMAP to RISC-V MMU in *Sv39*-mode, developed trap handlers for interrupts and exceptions, implemented routines for process fork and context switch, and developed drivers to probe and attach machine-dependent devices. With these efforts, the OpenBSD kernel can boot on a QEMU-emulated RISC-V hardware target up through entry into the init process.

# ACKNOWLEDGMENTS

We would like to thank our advisor, Michael Larkin. His expertise with OpenBSD has been essential to the team's success in both the implementation and bring-up of the OpenBSD operating system on RISC-V.

# TABLE OF CONTENTS

| Lis | st of Tables                                                                                                                                                                                                                                                    | ix                                                                             |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Lis | st of Figures                                                                                                                                                                                                                                                   | x                                                                              |

| 1   | Introduction.1.1RISC-V.1.2OpenBSD.1.3Justification                                                                                                                                                                                                              | 1<br>1<br>2<br>3                                                               |

| 2   | Technologies Description2.1Toolchain2.1.1LLVM2.1.1.1Clang2.1.1.2LLD2.1.2QEMU2.1.3GDB2.2RISC-V2.2.1Privilege Modes2.2.1.2Supervisor-Mode2.2.1.3User-Mode2.2.2Execution Environments2.2.2.1Supervisor Execution Environment2.2.2Application Execution Environment | 4<br>4<br>4<br>5<br>6<br>7<br>7<br>7<br>8<br>9<br>9<br>9<br>9<br>9<br>10<br>11 |

| 3   | Project Overview3.1Development Environment3.2Functional Requirements3.2.1Essential3.2.2Desired3.2.3Optional3.3Non-functional Requirements3.3.1Essential3.3.2Desired3.3.3Optional3.4Milestones3.5Dependencies                                                    | 12<br>12<br>12<br>12<br>13<br>13<br>13<br>13<br>13<br>13<br>14<br>15           |

| 4   | Project Architecture4.1Overview                                                                                                                                                                                                                                 | 17<br>17                                                                       |

|   | 4.2 Boc     | otstrap Subsystems                      | 18 |

|---|-------------|-----------------------------------------|----|

|   | 4.2.1       | Stage 1 Bootstrap: Hardware Reset       | 18 |

|   | 4.2.2       | Stage 2 Bootstrap: Berkeley Bootloader  | 19 |

|   | 4.2.3       | Stage 3 Bootstrap: OS Kernel Bootstrap  | 20 |

|   | 4.3 Mer     | mory Subsystem                          | 21 |

|   | 4.4 Traj    | p Subsystem                             | 24 |

|   | 4.4.1       | Trap CSRs                               | 25 |

|   | 4.4.2       | Trap Entry and Exit                     | 27 |

|   | 4.5 Proc    | cess Subsystem                          | 29 |

|   | 4.6 Dev     | rice Subsystem                          | 31 |

| 5 | Project Imp | plementation                            | 34 |

|   | 5.1 Dev     | Pelopment Environment Setup             | 34 |

|   | 5.1.1       | OpenBSD Machine                         | 34 |

|   | 5.1.2       | RISC-V Cross-Toolchain                  | 34 |

|   | 5.1.3       | QEMU                                    | 36 |

|   | 5.1.4       | GDB                                     | 37 |

|   | 5.2 Mac     | chine-Dependent Headers                 | 37 |

|   | 5.2.1       | Types (_ <i>types.h</i> )               | 37 |

|   | 5.2.2       | Atomics ( <i>atomic.h</i> )             | 38 |

|   | 5.2.3       | Endianness (endian.h)                   | 38 |

|   | 5.2.4       | Trap Frames (frame.h)                   | 39 |

|   | 5.2.5       | RISC-V Registers ( <i>riscvreg.h</i> )  | 40 |

|   | 5.2.6       | Process Control Block (pcb.h)           | 40 |

|   | 5.3 Earl    | ly Bootstrap Implementation             | 40 |

|   | 5.3.1       | Starting State                          | 41 |

|   | 5.3.2       | Resolve Kernel Physical Base Address    | 42 |

|   | 5.3.3       | Determine Boot HART                     | 42 |

|   | 5.3.4       | Set up Page Table                       | 42 |

|   | 5.3.5       | Set up Supervisor Trap Vector           | 44 |

|   | 5.3.6       | Jump to C Routine                       |    |

|   | 5.4 Mei     | mory Subsystem Implementation           |    |

|   | 5.4.1       | Bootstrapping the MMU                   |    |

|   | 5.4.2       | Initializing the Physical Map           | 47 |

|   | 5.4.3       | Creating a Page Table                   | 50 |

|   | 5.4.4       | Activating a Page Table                 | 52 |

|   | 5.4.5       | Updating a Page Table                   | 53 |

|   | -           | p Subsystem Implementation              | 57 |

|   | 5.5.1       | Routing a Trap                          | 57 |

|   | 5.5.2       | Interrupt Handling                      | 59 |

|   | 5.5.        | 1                                       | 60 |

|   | 5.5.        | 2.2 Platform-Level Interrupt Controller | 62 |

|    |          | 5.5.2.3  | HART-Level Interrupt Controller             | 63 |

|----|----------|----------|---------------------------------------------|----|

|    |          | 5.5.2.4  | Timer Interrupt Handling                    | 63 |

|    |          | 5.5.2.5  | External Interrupts Handling                | 64 |

|    | 5.5      | .3 Ex    | ception Handling                            | 65 |

|    |          | 5.5.3.1  | Instruction Faults                          | 66 |

|    |          | 5.5.3.2  | Memory Faults                               | 67 |

|    | 5.6      | Process  | Subsystem Implementation                    | 69 |

|    | 5.6      | .1 Pro   | ocess Fork                                  | 71 |

|    | 5.6      | .2 Co    | ontext Switch                               | 72 |

|    | 5.7      | Device   | Subsystem Implementation                    | 74 |

|    | 5.7      | .1 Ma    | ainbus                                      | 74 |

|    | 5.7      | .2 UA    | ART                                         | 76 |

|    | 5.7      | .3 HA    | ART                                         | 78 |

|    | 5.7      | .4 Ti    | mer                                         | 80 |

|    | 5.7      | .5 HA    | ART-Level Interrupt Controller              | 82 |

|    | 5.7      | .6 Sin   | mplebus                                     | 84 |

|    | 5.7      |          | atform-Level Interrupt Controller           | 85 |

|    |          |          |                                             |    |

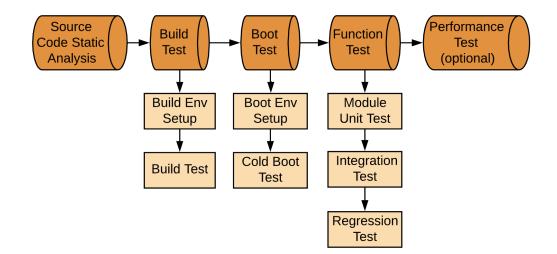

| 6  | Project  | Testing  | and Verification                            | 88 |

|    | 6.1      | Build T  | est                                         | 88 |

|    | 6.2      | Boot Te  | est                                         | 89 |

|    | 6.3      | Functio  | n Test                                      | 89 |

|    | 6.3      | .1 M     | odule Unit Test                             | 89 |

|    | 6.3      | .2 Sy    | stem Integration Test                       | 90 |

|    |          |          |                                             |    |

| 7  | Summa    | ary, Con | clusions, and Recommendations               | 91 |

|    | 7.1      | Summa    | ry                                          | 91 |

|    | 7.2      | Conclus  | sions                                       | 92 |

|    | 7.3      | Recom    | nendations for Further Development          | 92 |

|    |          |          |                                             |    |

| Re | ferences |          |                                             | 94 |

|    |          |          |                                             |    |

| Aţ |          |          | ce Definition and Configuration Source Code | 96 |

|    | A.1      | Device   | Definition Code                             | 96 |

|    | A.2      | Device   | Configuration Code                          | 97 |

|    | A.3      | Auto-ge  | enerated Device Configuration Table         | 97 |

# LIST OF TABLES

| Table 1. | Supported Combinations of RISC-V Privilege Modes     | 8  |

|----------|------------------------------------------------------|----|

| Table 2. | RISC-V Supervisor Cause Register (scause) after Trap | 28 |

| Table 3. | Summary of RISC-V Supervisor-Mode Exception Types    | 65 |

# LIST OF FIGURES

| Fig. 1.  | Components of three-phase compiler                            | 4  |

|----------|---------------------------------------------------------------|----|

| Fig. 2.  | LLVM's modular approach to the three-phase compiler           | 5  |

| Fig. 3.  | LLD combines OpenBSD kernel modules into an executable binary | 6  |

| Fig. 4.  | Remote debugging QEMU via the GDB stub                        | 7  |

| Fig. 5.  | HW-OS-App three layer hierarchy.                              | 8  |

| Fig. 6.  | SEE-AEE-App three layer hierarchy.                            | 10 |

| Fig. 7.  | OS connects hardware and applications                         | 17 |

| Fig. 8.  | Decomposition of machine-dependent kernel layer.              | 18 |

| Fig. 9.  | Multi-layer memory management system                          | 22 |

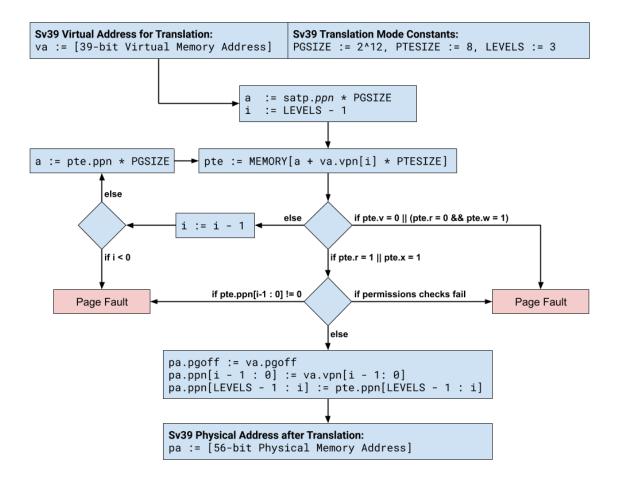

| Fig. 10. | The Sv39 memory address translation state machine             | 23 |

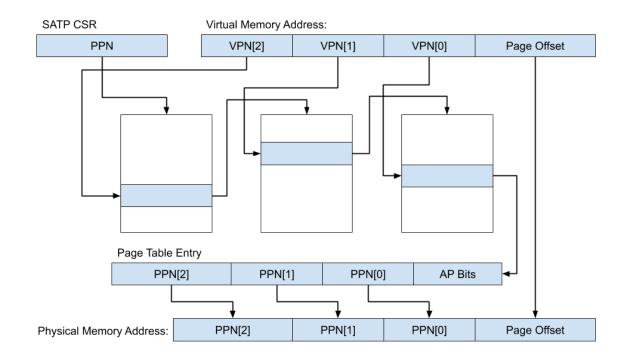

| Fig. 11. | Sv39 memory address translation for a 4 KiB page              | 24 |

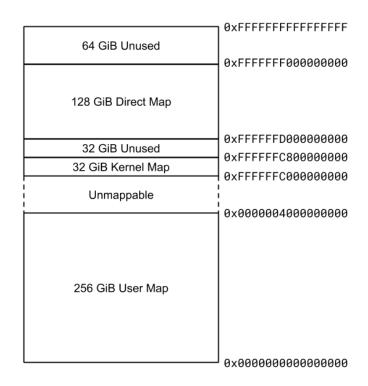

| Fig. 12. | Virtual address space layout (Sv39) for the ported OpenBSD    | 25 |

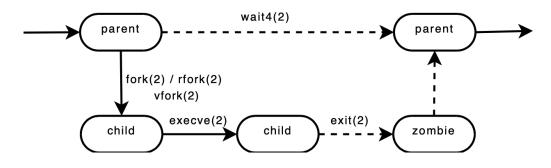

| Fig. 13. | Managing processes via system calls                           | 30 |

| Fig. 14. | Save and restore execution states in a context switch         | 31 |

| Fig. 15. | The device attachment hierarchy                               | 33 |

| Fig. 16. | One possible setup of the develop environment                 | 38 |

| Fig. 17. | OpenBSD early bootstrap control flow on RISC-V                | 41 |

| Fig. 18. | The initial page table at bootstrap stage                     | 43 |

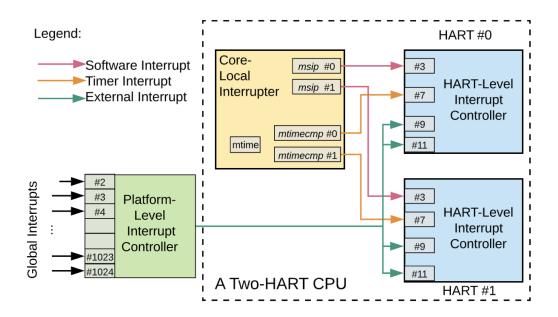

| Fig. 19. | A two-level nested interrupt controller architecture.         | 60 |

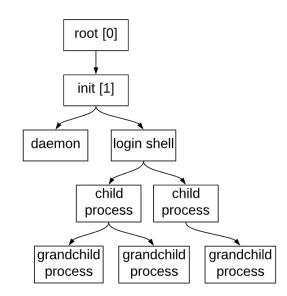

| Fig. 20. | Example of process hierarchy in a UNIX-like system.           | 71 |

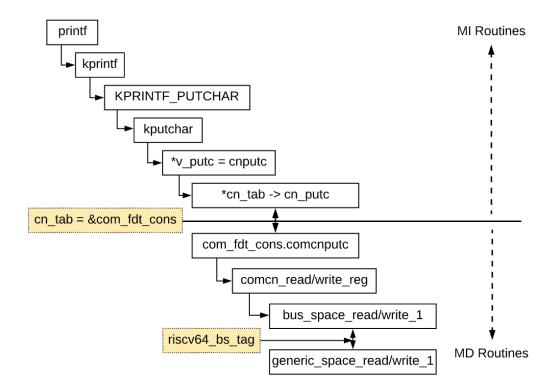

| Fig. 21. | The MI-MD interface for printf                                | 77 |

| Fig. 22. | Project quality assurance flow.                               | 88 |

#### **1 INTRODUCTION**

# 1.1 RISC-V

RISC-V is an Instruction Set Architecture (ISA) whose development was started by UC Berkeley in 2010 [1]. The RISC-V ISA is open-source and royalty-free and does not carry the same restrictive licensing burden as other ISAs, including x86 and ARM. Developer manuals and documentation for the RISC-V ISA are made available for free from the RISC-V Foundation which owns, maintains, and publishes documents for all intellectual property pertaining to the RISC-V ISA.

The RISC-V ISA follows a modular design philosophy which aims to be both flexible and versatile for a broad range of different applications. The RISC-V ISA defines two frozen base instruction sets<sup>1</sup>, RV32I and RV64I, which provide only a limited set of integer instructions. All other ISA features come as extensions [2] to the base instruction set. These extensions provide general purpose features such as multiplication and division (M), atomic instructions (A), single-precision floating-point (F), and double-precision floating-point (D). The set of features supported by a particular implementation of the RISC-V ISA are identified by its implementation identifier.

ISA-level modularity gives control back to vendors to choose an implementation that best fits their specific application. Embedded platforms might implement RV32EC — the 32-bit base instruction set optimized for embedded systems with support for compressed format instructions — to optimize for a smaller silicon footprint and lower power consumption. More powerful machines intended to run a full-fledged operating system might implement RV64GC which provides a useful set of features for general purpose computing.

<sup>1.</sup> The RISC-V ISA also defines two additional base instruction sets: RV32E and RV128I. The former reduces the number of registers from the RV32I base instruction set for embedded platforms and the latter includes 128-bit support. Unlike RV32I and RV64I, these two base instruction sets are not yet ratified.

The RISC-V ISA has an advantage over older ISAs due to the benefit of hindsight. RISC-V incorporates ideas learned from other popular instruction sets that have had multiple decades to mature in the marketplace [3]. Unlike more mature instruction sets, the RISC-V ISA is not bogged down by decades-worth of backward compatibility over multiple generations of hardware.

The RISC-V ISA also benefits from its openness and transparency. Unlike other ISAs whose implementation details are obscured behind non-disclosure agreements, the RISC-V ISA adopts a model which encourages collaboration. A number of open-source implementations of the RISC-V ISA are already available for experimentation [4]. Open-source hardware implementations benefit from the diverse perspectives of their individual contributors which help harden the hardware against security threats over time. Combining a hardened open-source hardware platform with a hardened operating system kernel (e.g., OpenBSD) will lead to the development of noticeably more secure systems.

The RISC-V ISA is not without its weaknesses, of which its newness is a major one. Unlike well-established ISAs, the RISC-V ISA is just starting to gain traction in commercial applications and has not yet seen widespread adoption. The lack of adoption can be attributed to both the newness of the architecture and lack of software support for RISC-V. Only a handful of operating systems, including FreeBSD and Linux, have been updated to support the RISC-V ISA. The majority of operating systems do not support RISC-V yet. OpenBSD is one of them.

#### 1.2 OpenBSD

OpenBSD is a Unix-like operating system which descends from the Berkeley Software Distribution (BSD) series of operating systems. OpenBSD was forked in 1995 from NetBSD by Theo de Raadt. Since then, OpenBSD has become renowned for its strong security principles and contributions to open-source software, for example, OpenSSH.

2

OpenBSD puts decades worth of security research and development into practice and prides itself on its strong security record. OpenBSD touts itself as one of the most secure operating system kernels available on the market today. Its strong security record is maintained through the practice and application of a number of methodologies, including:

- Comprehensive file-by-file audits of all critical software components.

- Proactive endeavors to identify and address bugs even if not proven exploitable.

- Applying strong security settings in the default operating system install.

- Limiting the default set of active services to reduce attack surface.

Despite OpenBSD's persistent focus on security, a number of relatively recent hardware-level security issues, including Spectre [5] and Meltdown [6], have shown that software systems are only demonstrably as secure as their underlying hardware platforms. This brings into question the security practices of existing hardware platforms and whether existing architectures can adapt to a changing security landscape.

# 1.3 Justification

The rise in prevalence of obscure hardware-level security problems in recent years has come to show that security is not a single faceted problem and cannot be completely addressed from within a single context. The security of software platforms such as the OpenBSD operating system depends heavily on the security of their underlying hardware platforms. The RISC-V ISA's promise to remain truly open and transparent is expected to help lead the development of security-hardened hardware platforms. This project takes the first step in that direction by porting a full OpenBSD operating system to the RISC-V ISA, starting with the OpenBSD kernel.

#### **2** TECHNOLOGIES DESCRIPTION

# 2.1 Toolchain

#### 2.1.1 LLVM

The LLVM Project is a collection of modular and reusable compiler and toolchain technologies [7]. Both LLVM and the GNU Compiler Collection (GCC) support the RISC-V ISA as of their latest releases. LLVM is leveraged in this project in large part due to a general trend seen across the BSDs moving away from GCC in favor of LLVM<sup>2</sup>. More importantly, RISC-V has been promoted from an experimentally-supported target to an officially-supported target starting with LLVM 9.

The LLVM Project toolchain provides a vast suite of build tools such as a C compiler (Clang), linker (LLD), debugger (LLDB), and more. This section focuses on only the subset of these tools which were critical to successfully porting the OpenBSD kernel.

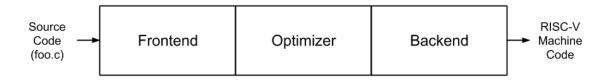

2.1.1.1 Clang: The front-end compiler infrastructure of the LLVM Project for C and C-based languages [10]. The Clang compiler differs from GCC, its GNU counterpart, in its modular approach to the three-phase compiler pipeline. A three-phase compiler consists of a front end, an optimizer, and a back end as shown in Figure 1.

Fig. 1. Components of three-phase compiler.

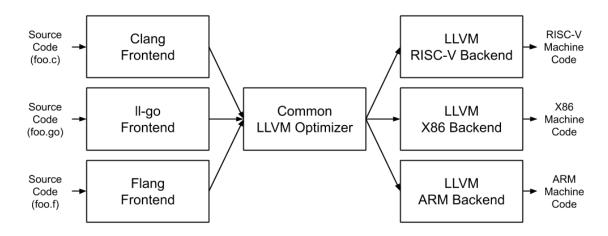

The LLVM utilizes a modular approach to break the pipeline into three independent phases. Clang is one example of a language front end for the LLVM compiler toolchain. It is responsible for transforming C-based source code into LLVM Intermediate

2. FreeBSD fully transitioned to LLVM in 2012 [8] and OpenBSD's x86 variant transitioned to LLVM in 2017 [9].

Representation (IR). LLVM IR is a low-level RISC-like virtual instruction set which represents a program as it passes through the optimizer and the back end of the LLVM compiler pipeline. IR is the key to LLVM's modularity. A front end can be written to leverage the existing LLVM common optimizer and back end. Similarly, a new back end can be written to generate machine code for a new target machine with a specific architecture, such as the RISC-V ISA.

Fig. 2. LLVM's modular approach to the three-phase compiler.

In this project, LLVM is leveraged as the cross-toolchain for building the OpenBSD kernel for the RISC-V architecture. The LLVM toolchain compilation procedure and patches added in this project are further detailed in Section 5.1.2.

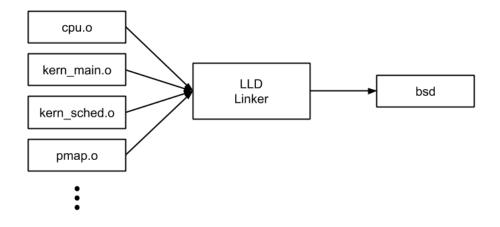

2.1.1.2 LLD: The platform-independent linker provided by the LLVM compiler toolchain. LLD is responsible for combining the machine code modules and libraries produced by the Clang front-end compiler into an executable format. It is designed as a drop-in replacement for the GNU linker which makes it easy to be inserted into the build process.

LLD is leveraged in this project to combine all machine-independent and machine-dependent kernel modules into a single compiled OpenBSD kernel file (bsd) as shown in Figure 3.

Fig. 3. LLD combines OpenBSD kernel modules into an executable binary.

# 2.1.2 QEMU

QEMU is a flexible open source machine emulator and virtualizer [11]. QEMU can perform a full system emulation of non-native hardware targets. For RISC-V, QEMU supports emulating either a generic virtual hardware platform or some commercially available developer kits such as the SiFive Freedom Unleashed U540 platform. QEMU support for RISC-V architecture is described in more detail in [12].

Hardware virtualization is essential to success of this project due to lack of access to physical RISC-V hardware. Whereas 64-bit x86 processors are easily accessible via cloud providers, RISC-V hardware is not yet widely available through consumer channels. Even though companies such as SiFive sell RISC-V hardware development kits, these kits are still much more expensive than mass-produced hardware based on x86 or ARM. Hence QEMU is utilized as a substitute for real RISC-V hardware to run and debug the ported OpenBSD kernel.

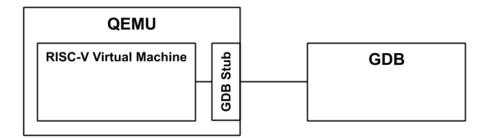

### 2.1.3 GDB

The GNU Debugger (GDB) is a powerful debugging tool that supports a number of target architectures. GDB provides useful commands to inspect, single-step, and debug applications. Most importantly, GDB offers functionality to perform remote debugging which enables debugging virtual RISC-V targets via the QEMU GDB stub as shown in Figure 4.

Fig. 4. Remote debugging QEMU via the GDB stub.

GDB was selected as the remote debugger for this project despite the heavy investment in the LLVM toolchain. In practice, GDB proved to be more reliable than the LLVM equivalent for remote debugging the OpenBSD kernel via the QEMU GDB stub.

# 2.2 RISC-V

#### 2.2.1 Privilege Modes

Privilege modes are a hardware-level security mechanism provided by the RISC-V ISA. This mechanism plays an important role in providing isolation between different software layers. The *RISC-V Privileged Architecture Specification* defines three privilege modes: *Machine (M) mode, Supervisor (S) mode,* and *User (U) mode.*

Not all implementations of the RISC-V ISA support all these three privilege modes. An embedded system, for example, typically only implements one or two of these privilege modes as shown in Table 1. Systems intending to run a full Unix-like operating system such as OpenBSD need to implement all three privilege modes.

| Number of Levels | Supported Modes | Intended Usage                              |

|------------------|-----------------|---------------------------------------------|

| 1                | М               | Simple embedded systems                     |

| 2                | M, U            | Secure embedded systems                     |

| 3                | M, S, U         | Systems running Unix-like operating systems |

Table 1Supported Combinations of RISC-V Privilege Modes

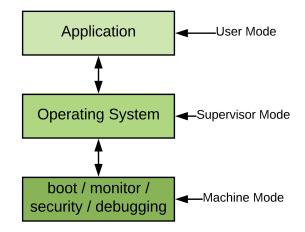

The privilege modes defined by the RISC-V ISA are strictly ordered. A higher privilege mode has access to a superset of features and permissions granted by all lower privilege modes. For example, Machine-level instructions can only be executed in machine-mode. However, user-level instructions can be executed in machine-mode, supervisor-mode, and user-mode. Virtual memory address translation is the only exception to this rule in that it is supported in supervisor-mode and user-mode but not machine-mode. The role of each privilege mode within the context of a system running a traditional operating system is illustrated in Figure 5.

Fig. 5. HW-OS-App three layer hierarchy.

2.2.1.1 Machine-Mode: The highest privilege mode intended for bare-metal / first-stage bootloader usage. Machine-mode provides unfettered access to the entire machine. All RISC-V HARTs (short for HARdware Thread) start in machine-mode and

can drop into lower privilege modes when entering lesser-privileged software layers. Within the scope of this project, the Berkeley Boot Loader (BBL) runs in machine-mode and is responsible for dealing with traps to machine-mode triggered by the lower privilege modes. BBL loads the OpenBSD kernel into system memory and drops into supervisor-mode upon entry into the OpenBSD kernel.

2.2.1.2 Supervisor-Mode: The middle privilege mode intended for operating system usage. Supervisor-mode provides access to most privileged instructions and system I/O functions and supports changing the virtual memory address translation scheme. Within the scope of this project, the OpenBSD kernel runs in supervisor-mode and is responsible for dealing with traps triggered by user-mode processes. The OpenBSD kernel loads user programs into system memory and drops into user-mode when entering a user process.

2.2.1.3 User-Mode: The lowest privilege mode intended for conventional application usage. User-mode is restrictive and is largely controlled by the operating system kernel which runs in supervisor-mode. User-mode applications are given access to unprivileged instructions and access system devices indirectly via the operating system kernel. Within the scope of this project, user-mode processes spawned by the OpenBSD kernel run in user-mode. The OpenBSD kernel running in supervisor-mode is given fine-grained control over user-mode processes.

#### 2.2.2 Execution Environments

An execution environment refers to the context under which some piece of software runs. A piece of software interacts with its execution environment via a binary interface, which defines the set of instructions and higher-level functions provided by the execution environment. RISC-V software remains portable across execution environments which implement a specific binary interface.

9

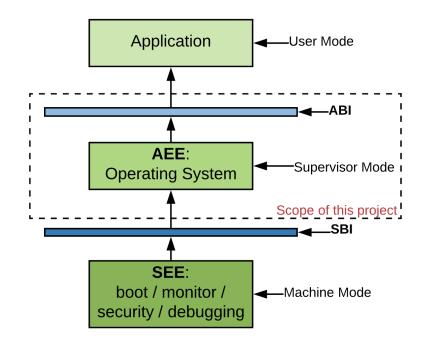

Porting an operating system to RISC-V involves dealing with two execution environments: the Supervisor Execution Environment (SEE) and the Application Execution Environment (AEE). The relationship between these environments and the operating system is shown in Figure 6.

Fig. 6. SEE-AEE-App three layer hierarchy.

2.2.2.1 Supervisor Execution Environment: The supervisor execution environment is the context under which an operating system executes. The SEE can be a simple bootloader or a hypervisor-provided virtual machine. An operating system interacts with its SEE via the Supervisor Binary Interface (SBI) which comprises the user-level and supervisor-level ISA along with a defined set of SBI functions [13]. The SBI represents the compatibility layer between an operating system and its SEE. An operating system binary compiled for a single SBI can be run on any SEE as long as the SEE exposes the correct SBI. In this project, the OpenBSD kernel is adapted to the SBI exposed by the Berkeley Boot Loader SEE. 2.2.2.2 Application Execution Environment: The application execution environment is the context under which user-mode programs execute. AEE is normally provided by an operating system such as OpenBSD. Similar to SEE, AEE exposes an Application Binary Interface (ABI) which comprises the user-level ISA and a defined set of ABI function calls, often referred to as system calls (or syscalls for short). The ABI varies across operating systems but is generally stable between releases of an operating system. The portability of an application binary is limited only by the target ABI. The OpenBSD AEE and ABI are touched upon in the implementation of the machine-dependent aspects of the OpenBSD kernel system call handler.

## **3 PROJECT OVERVIEW**

#### **3.1** Development Environment

- A host machine running OpenBSD for source code editing and compilation.

- A cross-toolchain to compile kernel source code to non-native RISC-V targets.

- A virtual or physical RISC-V hardware platform with Memory Management Unit (MMU) support for Sv39<sup>3</sup>.

- A bootloader providing the supervisor execution environment for the OS kernel.

- A debugger to remotely debug a RISC-V hardware target and inspect the kernel.

#### **3.2 Functional Requirements**

# 3.2.1 Essential

- Provide "config(8)"-syntax based kernel configuration.

- Provide "*files.config*(5)"-based file lists for Makefile generation.

- Construct machine-dependent kernel components to provide machine-independent kernel components with an interface to hardware, including:

- System Bootstrap

- System Memory Management

- Kernel and User Process Management

- Interrupt and Exception Handling

- Device Configuration and Management

- Boot OpenBSD kernel to copyright message on virtual RISC-V hardware platform.

# 3.2.2 Desired

- Support Symmetric Multi-Processing (SMP) for multi-processor RISC-V hardware.

- Boot OpenBSD kernel to copyright message on physical RISC-V hardware platform.

<sup>3.</sup> Sv39 refers to the page-based virtual memory address translation mode that supports 39 addressable bits of virtual memory address space. Sv48, which appears later in this report, refers to the page-based virtual memory address translation mode that supports 48 addressable bits of virtual memory address space.

# 3.2.3 Optional

- Cross-compile OpenBSD userland components (libc, libcompiler\_rt, etc.)

- Boot OpenBSD kernel through to multi-user login prompt on RISC-V hardware.

- Bootstrap build toolchain inside OpenBSD running on RISC-V hardware.

- Provide working OpenBSD RISC-V install media.

- Publish one or more compiled software binaries for OpenBSD on RISC-V.

- Add device support for non-essential RISC-V hardware devices.

# 3.3 Non-functional Requirements

- 3.3.1 Essential

- Standardization

- Adhere to *POSIX* and *ANSI* standards.

- Quality

- Discourage use of hacks and workarounds.

- Adhere to OpenBSD source code auditing guidance.

- Provide well-documented source code.

- 3.3.2 Desired

- Stability

- OpenBSD kernel remains stable under steady-state operation.

- Security

- Apply security best practices while implementing kernel code.

#### 3.3.3 Optional

- Performance

- Keep OpenBSD kernel overhead to a minimum, if possible.

- Consistency

- Keep the "look and feel" of OpenBSD on RISC-V consistent with other ISAs.

#### 3.4 Milestones

The primary goal of this project is to port the OpenBSD kernel to the RISC-V ISA. A number of smaller milestones pave the way to this goal and beyond. These milestones track work items from early development environment setup through stretch goals which identify nice-to-have features that are not considered critical to a successful OpenBSD kernel port. The milestones are enumerated below:

- 1) Development Environment

- a) Configure and build Clang+LLVM toolchain with support for the RISC-V ISA.

- b) Configure and build QEMU with support for emulating RISC-V hardware.

- c) Configure and build BBL to serve as bootloader for the OpenBSD kernel.

- d) Configure and build GDB to remotely debug the OpenBSD kernel on QEMU.

- 2) OpenBSD Kernel Source Tree

- a) Populate OpenBSD tree with minimum viable RISC-V kernel build boilerplate.

- b) Stub out required machine-dependent headers and source files for kernel build.

- c) Define, derive, or otherwise write out machine-dependent code, including:

- Early machine initialization code (*locore.S*)

- Standard system data types

- RISC-V machine registers

- System exception & interrupts handlers

- Per-CPU information structure

- Process control structures

- Stack frames for trap, exception, signal, context switch, etc.

- Memory management structures

- RISC-V hardware device drivers

#### 3) OpenBSD Kernel Cross-Compilation & Linking

a) Resolve remaining unresolved kernel symbols during initial kernel compilation.

- b) Generate OpenBSD RISC-V kernel binary using RISC-V cross-toolchain.

- c) Build BBL with OpenBSD RISC-V kernel payload.

- 4) OpenBSD Kernel Bring-up

- a) Hack at kernel implementation until OpenBSD kernel boots to copyright message.

- b) Boot OpenBSD through autoconf (device probing and configuration)

- c) Bring up additional system devices, including:

- Virtual block devices (e.g., VIRTIO BLK, the VirtIO Block Driver)

- Virtual network device (e.g., VTNET, the VirtIO Ethernet Driver)

- d) Fork and exec to init process

- 5) OpenBSD Multi-User [Stretch Goal]

- a) Build OpenBSD userland components

- b) Support Simultaneous Multi-Processing (Optional)

- 6) OpenBSD RISC-V Installer & Bootloader [Stretch Goal]

- a) Write Installer for the RISC-V OpenBSD Port

- b) Write Bootloader for the RISC-V OpenBSD Port

#### 3.5 Dependencies

Porting the OpenBSD kernel to RISC-V carries a number of external dependencies, particularly around the availability of tooling that supports the RISC-V ISA. The RISC-V ISA is incredibly new relative to the other mainstream ISAs. The Intel x86 family of ISAs goes back as far as 1978 and the ARM ISA dates back to 1985. These ISAs have had plentiful time to mature and grow their market share over a few decades. Support for the RISC-V ISA, while growing, is still largely experimental across various virtualization products and build tools.

The success of this project depended heavily on support for the RISC-V ISA in virtualization tools such as QEMU. Companies including SiFive have made great strides in building out hardware platforms for RISC-V development. Unfortunately, these

development platforms are far too expensive to justify for purchase within the scope of this project. Instead, QEMU allows for emulation of virtual RISC-V hardware targets which are sufficient for kernel bootstrapping. While efforts to support the RISC-V ISA in QEMU only began in early 2018, other BSD-based operating systems including FreeBSD were successful in bootstrapping their operating system kernels on QEMU's virtual RISC-V hardware. As such, it is optimistic that QEMU's support for virtual RISC-V hardware targets would also be suitable in the work to bootstrap the OpenBSD kernel on RISC-V.

In addition to virtualization tools, the success of this project depended on support for the RISC-V ISA in build toolchains such as LLVM. The decision to bootstrap with the LLVM instead of GNU toolchain did carry some risk at the early stages of the project as LLVM support for the RISC-V ISA was still considered experimental until September 2019. The availability of the GNU toolchain as a fallback to LLVM helped to reassure that this project would not come to a complete standstill due to toolchain issues.

#### **4 PROJECT ARCHITECTURE**

#### 4.1 Overview

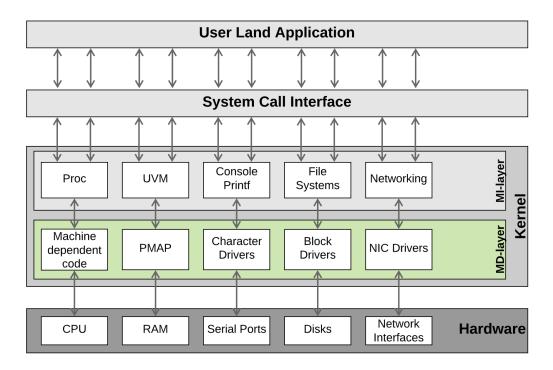

Operating systems are responsible for interfacing high-level applications with the low-level hardware resources provided by a computer system. The OS kernel serves user-mode applications by exposing a well-documented set of functions via an application binary interface which sits atop the machine-independent (MI) layer of the kernel. The MI layer of the OS kernel relies on a machine-dependent (MD) layer which provides abstractions over the underlying hardware resources. This multi-layer hierarchy is depicted in Figure 7.

Fig. 7. OS connects hardware and applications.

Porting an existing OS to a new architecture is a very different problem than writing an OS from scratch. The former focuses almost entirely on the MD layer of the OS kernel. The basic strategy involves rewriting the architecture-specific routines and drivers of the MD layer to provide an interface to the hardware for the MI layer. The MI layer remains largely unchanged. OpenBSD's MD layer can be divided into five subsystems, as shown in Figure 8. These subsystems are summarized in the sections that follow. Fine-grained implementation details for each are presented in Section 5.

| Bootstrap         | Memory           | Trap               | Process        | Device   |

|-------------------|------------------|--------------------|----------------|----------|

| Set up paging     | pmap_bootstrap() | Route a trap       | РСВ            | mainbus0 |

| Set up trap entry | pmap_create()    | Timer interrupt    | fork()         | cpu0     |

| Set up C runtime  | pmap_activate()  | External interrupt | Switchframe    | com0     |

| Handover to C     | pmap_enter()     | Instruction faults | Trapframe      | intc0    |

| Set up sigcode    | pmap_remove()    | Memory faults      | cpu_switchto() | plic0    |

Fig. 8. Decomposition of machine-dependent kernel layer.

# 4.2 Bootstrap Subsystems

Booting a Unix-like operating system on a RISC-V machine involves a multi-stage bootstrap process. For the OpenBSD operating system, the bootstrap process finishes upon entry into the MI OS kernel initialization routine. This bootstrap procedure can be divided into three stages:

- 1) Stage 1 Bootstrap: Hardware Reset

- 2) Stage 2 Bootstrap: Berkeley Boot Loader

- 3) Stage 3 Bootstrap: OS Kernel Bootstrap (OpenBSD)

### 4.2.1 Stage 1 Bootstrap: Hardware Reset

Stage 1 of system bootstrap begins from the moment that power is applied to a RISC-V processor. Applying power to the RISC-V circuitry generates a reset signal which places the hardware into a known starting state. For virtual hardware provided by

QEMU, this hardware reset is emulated in software. The routine that implements this, riscv\_cpu\_reset(), performs the following actions:

- Set privilege level to machine-mode.

- Set mstatus.MIE to 0 to disable interrupts.

- Set mstatus. MPRV to 0 to turns off address translation.

- Initialize mcause register to 0.

- Set pc to  $0 \times 00001000$  which targets the trampoline code in system ROM.

The trampoline code in system ROM acts as the first-stage bootloader. This small bit of code builds the Flattened Device Tree (FDT) to describe system hardware and loads the second-stage bootloader (BBL) into memory at address 0x80000000. The first-stage then yields control to the second-stage bootloader, passing along the address of the FDT.

# 4.2.2 Stage 2 Bootstrap: Berkeley Bootloader

The second stage of system bootstraps begins upon entry into the Berkeley Bootloader. BBL runs entirely in machine-mode, the highest RISC-V privilege mode, and provides the supervisor execution environment for the OS kernel. As described in paragraph 2.2.2.1, the combination of SEE and SBI is what allows a compiled kernel binary to remain portable across RISC-V hardware platforms. BBL abstracts away the underlying hardware and, instead, exposes a number of SBI functions which allow the OS kernel to interface with the machine-mode layer. BBL provides the following functionalities:

- Emulation of illegal instructions.

- A machine-mode trap handler for machine-level exceptions and interrupts.

- Routines to manage periodic timer interrupts.

- Chain loading and access to the initial console device.

As mentioned previously, the first stage of the system bootstrap process loads BBL at base address  $0 \times 80000000$ . The base address also serves as the entry point into BBL. Within the BBL executable, a reset\_vector is mapped to this base address which

kicks off the BBL bootstrapping process. This bootstrapping procedure performs roughly the following sequence of events:

- Selects one RISC-V HART to serve as the main HART for BBL. All other RISC-V HARTs are temporarily put to sleep until BBL is ready to transfer control to the OS kernel.

- Filters the FDT received from the previous-stage bootloader. This removes references to some hardware and other machine-specific details that are irrelevant during supervisor-mode operation.

- Wakes up all other HARTs from sleep. All HARTs join in executing the remaining steps up through OS kernel entry.

- 4) Reads mhartid Control and Status Register (CSR). The value read from this register is later passed to the OS kernel to uniquely identify each RISC-V HART.

- Configures physical memory permission (PMP) for supervisor-mode to allow full access to system memory resources.

- 6) Configures machine-mode trap handlers and stack. The BBL-provided trap handler code deals with machine-mode exceptions and interrupts.

- Drops the HART into supervisor-mode before jumping to the start of the BBL payload. In this project, the payload is a compiled OpenBSD kernel.

### 4.2.3 Stage 3 Bootstrap: OS Kernel Bootstrap

Stage 3 of system bootstrap begins upon entry into the OS kernel starting with *locore.S.* The OS kernel runs in supervisor-mode within the SEE provided by BBL. The kernel bootstrap procedure handles the bulk of the workload in preparing the system to initialize the OpenBSD kernel. This process includes:

- Setting up initial kernel page tables.

- Performing the switch into paged virtual memory mode.

- Probing and attaching hardware devices.

- Configuring the supervisor-mode trap handler.

- Initializing the global pointer and stack pointer.

- Propagating kernel arguments to the MI kernel.

- Jumping into the MI kernel initialization routine.

#### 4.3 Memory Subsystem

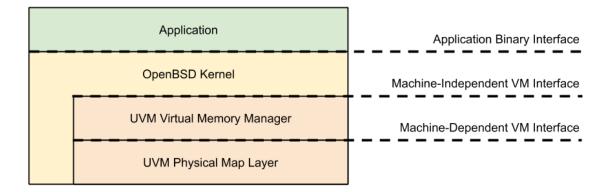

OpenBSD uses the UVM virtual memory system to manage system memory resources across multiple virtual memory address spaces [14]. UVM provides a high-level machine-independent view of system memory to the kernel as well as user-mode processes. UVM is a multi-layer system consisting of a large machine-independent layer, which manages virtual address spaces, and a lightweight machine-dependent layer, which serves as the interface to the system's Memory Management Unit.

The UVM external interface exposes high-level memory operations such as allocating pageable or non-pageable memory regions, setting permissions on those memory regions, and adjusting the size of allocated memory regions. Internally, the machine-independent layer of UVM manages software structures which represent the layout of the virtual address space for each process on the system. As necessary, the machine-independent layer delegates to the machine-dependent layer to insert or remove virtual-to-physical address mappings.

The machine-dependent layer modifies in-memory page tables which affect the virtual memory layout exposed by the MMU. The machine-dependent layer must understand the memory address translation schemes supported by the target architecture. The relationship between user-mode applications, the kernel, and the sub-layers of the memory management system is illustrated in Figure 9.

The 64-bit variant of the RISC-V ISA supports three memory address translation modes. As of publication of "*RISC-V Privileged Architecture Specification v1.11*", these modes include: Bare, Sv39, and Sv48. The specification also reserves two additional

Fig. 9. Multi-layer memory management system.

modes for future use: Sv57 and Sv64. The Bare mode provides a simple identity mapping between virtual and physical memory addresses without memory protection. The Sv39 and Sv48 modes are 4 KiB page-based memory address translation schemes.

In porting the OpenBSD kernel, only Sv39 mode is supported to keep a tight bound on complexity in the memory subsystem. Sv39 mode is similar in nature to the page-based memory schemes used in other architectures, such as 64-bit ARM. Sv39 mode uses a 3-level page table walk to translate a virtual address to a physical address. The virtual to physical address translation procedure for Sv39 is portrayed in Figure 10.

As shown in Figure 10, a virtual address with 39 addressable bits maps to a physical address of 56 addressable bits. During translation, a page fault can occur if an invalid entry is encountered or if a permissions check fails. Page faults which arise during user-mode operation will trigger a trap to the supervisor trap handler, which further delegates to UVM to resolve the fault. A page fault may be resolved by mapping a missing entry into the page table, or by terminating the process which triggered the fault. Assuming the virtual to physical address translation does not cause a page fault, the translation of a virtual address to a physical address can be visualized as in Figure 11.

22

Fig. 10. The Sv39 memory address translation state machine.

Virtual to physical address translation allows the OpenBSD kernel to share limited memory resources among a large number of resident processes. Each resident process is assigned a dedicated virtual address space identifier. The layout of each virtual address space is dictated by the layout as defined in the machine-dependent kernel source, and the layout is baked into the compiled kernel. This porting work inherits the virtual memory layout adopted by FreeBSD's RISC-V port. The virtual address space layout is depicted in Figure 12.

The Sv39 memory address translation mode provides 512 GiB of addressable virtual address space. The lowest 256 GiB of virtual address space is reserved for user-mode

Fig. 11. Sv39 memory address translation for a 4 KiB page.

processes. The highest 256 GiB of virtual address space is reserved for the kernel. 32 GiB of the kernel-reserved space, starting from 0xFFFFFFC000000000, is assigned to the *Kernel Map* to hold kernel code and data. Another 128 GiB of the kernel-reserved space, starting from 0xFFFFFD000000000, is assigned to the *Direct Map* which is an offset-identity mapping of physical memory. The remaining 96 GiB of kernel-reserved space is unused.

#### 4.4 Trap Subsystem

A trap is a form of synchronous event which causes a RISC-V HART to halt its current activities and immediately transfer control to a trap handler. This document focuses exclusively on supervisor-mode traps which are handled by the OpenBSD kernel. This document uses the terms *exception*, *interrupt*, and *trap* in alignment with the

24

Fig. 12. Virtual address space layout (Sv39) for the ported OpenBSD.

definitions provided by *The RISC-V Instruction Set Manual, Volume I: User-Level ISA* [15]:

- "we use the term *exception* to refer to an unusual condition occurring at run time associated with an instruction in the current RISC-V thread."

- "we use the term *interrupt* to refer to an external asynchronous event that may cause a RISC-V HART to experience an unexpected transfer of control."

- "we use the term *trap* to refer to the transfer of control to a trap handler caused by either an exception or an interrupt."

# 4.4.1 Trap CSRs

The CSRs provided by the RISC-V ISA that are used for supervisor-mode trap configuration and handling are listed below:

- The Supervisor Status (sstatus) Register contains some bits for controlling system trap behavior. This includes bits for controlling whether interrupts are enabled (SIE, UIE), bits for indicating whether interrupts were enabled prior to entering the supervisor-mode trap handler (SPIE, UPIE), and a bit for indicating the privilege mode prior to entering the supervisor-mode trap handler (SPP).

- The Supervisor Cause (scause) Register indicates the cause for a trap. This register dedicates one bit for distinguishing between traps caused by exceptions and traps caused by interrupts. The remaining bits are used to uniquely identify the exact type of exception or interrupt that occurred. This register takes on one of the states as enumerated in Table 2.

- The Supervisor Trap Value (stval) Register holds an exception-specific value that can be used by the trap handler to service the exception. During a misaligned instruction exception, for example, this register will hold the virtual address which triggered the exception.

- The Supervisor Trap Vector (stvec) Register holds the base address of trap vector and the trap vectoring mode. The trap vectoring supports *Direct*-mode and *Vectored*-mode.

- Direct-mode is the default value. In Direct-mode, stvec holds the base address

of the overall trap handler entry, and software is responsible for figuring out the

source of exception/interrupt and acting accordingly.

- Vectored-mode introduces a method to create a vector table that hardware uses to achieve lower interrupt handling latency. When an interrupt occurs in Vectored-mode, the pc will get assigned by the hardware to the address stored in the vector table entry corresponding to the interrupt ID.

- The Supervisor Interrupt Enable (sie) Register allows for specific subsets of interrupts to be enabled or disabled. These interrupts include software interrupts, timer interrupts, and external interrupts.

- The Supervisor Interrupt Pending (sip) Register contains information on pending interrupts. As with sie, these interrupts include software interrupts, timer interrupts, and external interrupts.

- The Supervisor Exception Program Counter (sepc) Register preserves the program counter (pc) at the moment the trap occurs. This register can be modified during trap handling to adjust the program counter upon return from the trap handler.

# 4.4.2 Trap Entry and Exit

RISC-V ISA specification aims to keep trap handling simple. The state of the hardware is largely unchanged upon entry into the supervisor trap handler. Both hardware and software benefit from this. Implementing trap handling in hardware is not only easier, but supervisor software does not have to work around hardware-level assumptions.

All traps to supervisor-mode arrive at the OS kernel via the kernel trap entry point installed in stvec during early bootstrap, as described in Section 5.3.5. Upon trap to the supervisor, the hardware needs to complete the following tasks [16]:

- Save pc to sepc.

- Save privilege mode to sstatus. SPP.

- Save sstatus.SIE to sstatus.SPIE.

- Set sstatus.SIE to  $\boldsymbol{0}.$

- Set scause to trap reason.

- Set stval with exception-specific value, if applicable.

- Set pc to trap handler base address which has been installed to stvec.

After making the state changes above, the hardware immediately begins executing the kernel trap handler code. The initial entry point into the kernel trap handler is

Table 2RISC-V Supervisor Cause Register (scause) after Trap

| Interrupt | Code  | Description                      |

|-----------|-------|----------------------------------|

| 1         | 0     | User software interrupt          |

| 1         | 1     | Supervisor software interrupt    |

| 1         | 2-3   | Reserved for future standard use |

| 1         | 4     | User timer interrupt             |

| 1         | 5     | Supervisor timer interrupt       |

| 1         | 6-7   | Reserved for future standard use |

| 1         | 8     | User external interrupt          |

| 1         | 9     | Supervisor external interrupt    |

| 1         | 10-15 | Reserved for future standard use |

| 1         | ≥16   | Reserved for platform use        |

| 0         | 0     | Instruction address misaligned   |

| 0         | 1     | Instruction access fault         |

| 0         | 2     | Illegal instructions             |

| 0         | 3     | Breakpoint                       |

| 0         | 4     | Load address misaligned          |

| 0         | 5     | Load access fault                |

| 0         | 6     | Store/AMO address misaligned     |

| 0         | 7     | Store/AMO access fault           |

| 0         | 8     | Environment call from U-mode     |

| 0         | 9     | Environment call from S-mode     |

| 0         | 10-11 | Reserved for future standard use |

| 0         | 12    | Instruction page fault           |

| 0         | 13    | Load page fault                  |

| 0         | 14    | Reserved for future standard use |

| 0         | 15    | Store/AMO page fault             |

| 0         | ≥16   | Reserved                         |

machine-dependent code provided by the OS kernel which performs the transition into the kernel. Since the changes to hardware state are limited, the kernel trap handler gets to decide what state is saved upon entry into the kernel.

In addition to supervisor-level trap CSRs, the Supervisor Scratch (sscratch) Register is often helpful in retaining state between entry into and exit from the kernel. The sscratch register has no ISA-designated purpose, and thus the OS kernel can use it for any purpose. Within the OpenBSD trap handler, this register is used to quickly swap between the user stack and the kernel stack upon entry into and exit from the kernel.

Once the state of the active process is saved and the kernel stack is switched onto the HART, the trap handler attempts to route the trap within the kernel. The kernel reads the scause register to identify the exact cause of the trap and delegates to the appropriate sub-handler.

Upon completion of trap handling, control may return to the faulting process. The state of the faulting process is restored onto the HART and an sret instruction triggers the hardware to switch back to the process at its appropriate privilege mode. This equates to the following steps:

- Restore privilege mode from sstatus.SPP.

- Restore sstatus.SIE from sstatus.SPIE.

- Restore pc from sepc.

### 4.5 Process Subsystem

The OpenBSD process subsystem is responsible for managing the life cycle of processes within the operating system. Each process is an instance of an executable program and operates in its own virtual address space. A process is represented in a software structure, an instance of "struct process" which retains relevant information about the process. The structure includes, among other things, a pointer to the virtual address space structure used by the memory subsystem to manage virtual to physical address mappings for the process.

Processes spawn from parent processes in response to certain syscalls provided by the kernel. Child processes are typically spawned by some combination of the fork() + exec() syscalls. An example of this is shown in Figure 13. The call to fork() generates a new child process which is nearly identical to its parent and is almost always

29

followed up by a call to exec() to load an executable and trigger Address Space Layout Randomization (ASLR).

Fig. 13. Managing processes via system calls.

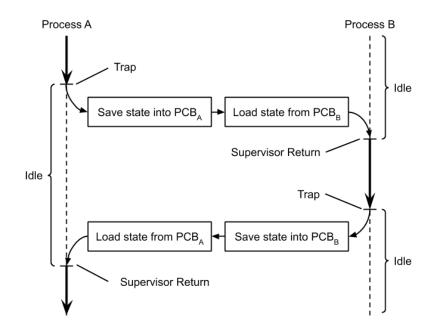

The OS kernel is responsible for managing access to hardware resources among processes. On a given system, there might be a hundred or more processes competing for access to just a handful of HARTs. To share HARTs between processes, the OS kernel time-slices access to the HARTs with help from a periodic hardware timer interrupt. Before a process is assigned to a HART, the OS kernel ensures that the periodic timer is primed so that a trap will eventually force the process to yield the HART back to the kernel scheduler. When the scheduling-related trap occurs, this signals to the kernel to swap out the active process for another process as seen in Figure 14.

The trap causes the state of the HART to be saved into the Process Control Block (PCB) to make way for a new process. The kernel scheduler selects another process to take control of the RISC-V HART. The previous state of the selected process is restored on the HART to complete the context switch into the new process. The machine-dependent aspects of the context switch are explored in more detail in Section 5.6.2.

Fig. 14. Save and restore execution states in a context switch.

### 4.6 Device Subsystem

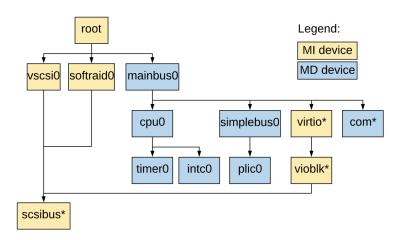

During system startup, the early system bootloaders enumerate system devices into a structure known as the FDT. The FDT describes system hardware including the RISC-V HARTs, the memory map, and the attached devices.

During OpenBSD initialization, the kernel runs through a process called *autoconf*. The FDT serves as a guide for the OS kernel to properly discover and configure hardware devices. During the *autoconf* process, the OS kernel traverses the FDT to match hardware devices with compatible drivers using the system configuration table, which is generated based on device definition in *files.riscv64* and device configuration in a file named *GENERIC*. The system configuration table describes the expected attachment points for various devices and associates them with an appropriate driver.

The *autoconf* process is recursive in nature. The process begins by traversing devices nodes attached at the root of the FDT. As device nodes are attached, their child nodes are

expanded and traversed. The key routines for the *autoconf* process are enumerated in Snippet 1.

```

void *

config_search(cfmatch_t func, struct device *parent, void *aux);

struct device *

config_attach(struct device *parent, void *match, void *aux, cfprint_t print)

struct device *

config_found_sm(struct device *parent, void *aux, cfprint_t print,

cfmatch_t submatch);

```

Snippet 1. autoconf key routines.

Given a parent device, config\_search() identifies the best-matched child device under a specific matching criteria. config\_attach() will then attach the child device to its parent in three steps. First, it allocates memory for the device's software configuration structure (config\_make\_softc()). This structure is then filled with this device's hardware information as parsed from FDT. Lastly, the device-specific initialization logic is performed as provided by the device driver. At this stage, this device's child device will get attached recursively.

config\_found\_sm() locates the configuration data for a device and attaches it. This boils down to making calls to config\_search() and config\_attach(), consecutively. autoconf supports two modes of configuration: *direct* mode and *indirect* mode. When a child device is provided via the aux argument, *direct* mode is used and the device is attached directly. Otherwise, *indirect* mode is used which scans the bus to match and attach a compatible device.

The device attachment hierarchy of this project is demonstrated in Figure 15. This project provides definition, configuration, and driver-level code for machine-dependent devices identified in this hierarchy. This is presented in Section 5.7.

Fig. 15. The device attachment hierarchy.

#### **5 PROJECT IMPLEMENTATION**

#### 5.1 Development Environment Setup

This section briefly describes how to set up a development environment for the purpose of porting OpenBSD to RISC-V ISA. An OpenBSD host machine is required for source code editing and kernel cross compilation. Cross-compilation tools are mandatory for building the OpenBSD kernel on an x86 host for a riscv64 target. The cross-compiled kernel is encapsulated as payload into BBL and runs on a QEMU virtual machine. GDB can then be attached to QEMU to single-step the OpenBSD kernel and inspect its functionality.

# 5.1.1 OpenBSD Machine

The OpenBSD machine can be bare-metal or a virtual machine. This machine is used for cross-compiling the OpenBSD kernel. The OpenBSD kernel building supports incremental compilation which reduces the time necessary to recompile the kernel for incremental updates to source code. However, some machine-dependent headers, such as *cpu.h*, are widely-referenced across the OpenBSD source tree. Modifications to widely-used headers can trigger re-compilation of large portions of the OpenBSD kernel which can drastically increase build time.

Running OpenBSD as a virtual machine on a cloud-provider allows for flexibility in tuning CPU and memory resources. The virtual machine can be scaled up for speed when running a full kernel build and scaled down for cost-saving when running incremental kernel builds. In this project, a customized OpenBSD installation image is created to install OpenBSD on a cloud-resident virtual machine [17].

# 5.1.2 RISC-V Cross-Toolchain

LLVM is selected as the RISC-V cross-toolchain for this project. The pre-compiled LLVM binaries in trusted OpenBSD-current software sources do not include stable support for RISC-V. Similarly, the latest version of LLVM in the OpenBSD ports repository predates the inclusion of RISC-V as a stable target. LLVM 9 is the first LLVM release to support RISC-V as an officially-supported, non-experimental target. In this project, LLVM is compiled from source to obtain a working LLVM 9 toolchain with support for RISC-V<sup>4</sup>. The build configuration used to produce the LLVM toolchain used in this project is shown in Snippet 2.

```

# Run from within ${LLVM_PROJECT_ROOT}/build

$ cmake \

-DLLVM_ENABLE_FFI:Bool=False \

-DLLVM_ENABLE_TERMINFO:Bool=False \

-DLLVM_ENABLE_RTTI:Bool=False \

-DCMAKE_DISABLE_FIND_PACKAGE_LibXml2:Bool=True \

-DCMAKE_DISABLE_FIND_PACKAGE_Z3:Bool=True \

-DLLVM_TOOL_LLDB_BUILD:Bool=True \

-DLLVM_BUILD_LLVM_DYLIB:Bool=True \

-DLLVM_LINK_LLVM_DYLIB:Bool=True \

-DGO_EXECUTABLE=GO_EXECUTABLE-NOTFOUND \

-DCMAKE_DISABLE_FIND_PACKAGE_Backtrace:Bool=True \

-DLLVM_TARGETS_TO_BUILD:String="X86;RISCV" \

-DLLVM_ENABLE_PROJECTS:String="clang" \

-DCMAKE_BUILD_TYPE=Release \

-DCMAKE_INSTALL_PREFIX=/usr/local/riscv \

-DCMAKE_CXX_FLAGS="-mno-retpoline" \

-G Ninja \

../llvm

$ ninja -j8

```

Snippet 2. CMake configuration for the LLVM cross-toolchain.

A patch to the LLVM toolchain was later applied to the LLVM toolchain to address missing pre-processor defines during initial kernel compile. The missing pre-processor defines were a side-effect of the LLVM toolchain not fully parsing the OpenBSD-specific compile target: --target=riscv64-unknown-openbsd6.7. This patch, shown in Snippet 3, was introduced to local copies of the LLVM toolchain source code to address this issue.

<sup>4.</sup> The toolchain used in the project was later upgraded to LLVM 10.

```

From ebd07b299e0c5e4d9cd0779861969b846fc8f2a6 Mon Sep 17 00:00:00 2001

From: Brian Bamsch <bbamsch@google.com>

Date: Mon, 14 Apr 2020 20:59:09 -0700

Subject: [PATCH] [RISCV] Add Target for OpenBSD

clang/lib/Basic/Targets.cpp

| 2 ++

clang/test/Preprocessor/init.c | 3 +++

2 files changed, 5 insertions(+)

diff --git a/clang/lib/Basic/Targets.cpp b/clang/lib/Basic/Targets.cpp

index c063f8ca447..bacc2149fbe 100644

--- a/clang/lib/Basic/Targets.cpp

+++ b/clang/lib/Basic/Targets.cpp

@@ -389,2 +389,4 @@ TargetInfo *AllocateTarget(const llvm::Triple &Triple,

return new LinuxTargetInfo<RISCV64TargetInfo>(Triple, Opts);

+

case llvm::Triple::OpenBSD:

+

return new OpenBSDTargetInfo<RISCV64TargetInfo>(Triple, Opts);

default:

diff --git a/clang/test/Preprocessor/init.c b/clang/test/Preprocessor/init.c

index 6966698549a..647563d92a9 100644

--- a/clang/test/Preprocessor/init.c

+++ b/clang/test/Preprocessor/init.c

@@ -9558,2 +9558,4 @@

// RUN:

| FileCheck -match-full-lines -check-prefixes=RISCV64,RISCV64-LINUX

\hookrightarrow %s

+// RUN: %clang_cc1 -E -dM -ffreestanding -fgnuc-version=4.2.1 -triple=riscv64-

→ unknown-openbsd < /dev/null \

+// RUN: / FileCheck -match-full-lines -check-prefixes=RISCV64,RISCV64-

↔ OPENBSD %s

// RISCV64: #define _LP64 1

@@ -9760 +9762,2 @@

// RISCV64-LINUX: #define unix 1

+// RISCV64-OPENBSD: #define __OpenBSD__ 1

2.26.0

```

Snippet 3. Diff of changes made to LLVM source to support 'riscv64-unknown-openbsd6.7'.

# 5.1.3 QEMU

QEMU provides the virtual RISC-V hardware target used to bootstrap the initial OpenBSD kernel port in this project. QEMU exposes a GDB stub which provides a convenient mechanism to single-step the kernel and debug issues during kernel initialization.

As explained in Section 4.2, supervisor-mode software such as the OpenBSD kernel is compiled against the standard supervisor binary interface to increase portability. The

OpenBSD kernel has to run within an SEE that exposes certain SBI functions. In this project, BBL is responsible for providing the SEE to the OpenBSD kernel. The BBL executable embeds the compiled OpenBSD kernel and sets up the appropriate SEE before handing over control to the kernel payload. This BBL executable is passed to QEMU via the kernel argument to boot the OS kernel.

# 5.1.4 GDB

The version of GDB shipped with OpenBSD-current does not support the RISC-V ISA. Therefore, GDB needs to be built from source. Unfortunately, building GDB on OpenBSD has been proved to be quite cumbersome. This issue is sidestepped by instead running GDB on a different machine and debugging QEMU remotely. This project's work repository [17]: '02-Set up RISCV-GNU tool chain on Linux & OpenBSD' provides a step-by-step guide for this.

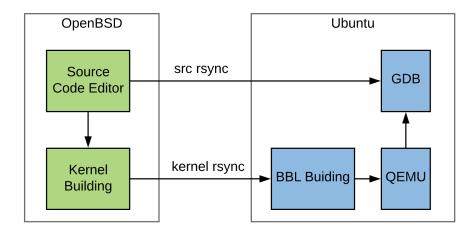

Figure 16 demonstrates a possible environment setup, where the OpenBSD machine is dedicated to source code editing and kernel compilation while a remote Ubuntu machine is utilized for building BBL, running QEMU, and debugging the kernel with GDB. BBL building and QEMU can also run on the OpenBSD host machine, which is functionally equivalent to the configuration in Figure 16.

### 5.2 Machine-Dependent Headers

The machine-dependent kernel components interface directly with the RISC-V hardware and provide the necessary bindings to the machine-independent kernel components. This section highlights a few of the relatively large set of machine-dependent interfaces that have been implemented to support the RISC-V ISA.

## 5.2.1 Types (\_types.h)

The Types header defines the machine-dependent data types. More specifically, it assigns the exact-width, minimum-width, fastest minimum-width, and greatest-width

Fig. 16. One possible setup of the develop environment.

integers to their appropriate underlying data types. This file also assigns types for register-sized data, physical memory addresses, and virtual memory addresses. The types defined in this file are used widely across the OpenBSD kernel.

# 5.2.2 Atomics (atomic.h)

The Atomics header defines a set of functions which are used to provide atomic updates to memory. In particular, this header exposes atomic\_setbits\_int and atomic\_clearbits\_int, which read a location from memory, set or clear bits present in an integer-sized mask, and write the value back to the same location in memory. This kernel header also provides memory barriers including: a barrier to wait on all pending reads from memory, a barrier to wait on all pending writes to memory, as well as a barrier to wait on all pending memory operations.

# 5.2.3 Endianness (endian.h)

The Endianness header interface provides a small set of functions to swap the endianness of values in memory. The RISC-V baseline architecture uses little-endian byte order but does not rule out the possibility for big-endian byte order implementations nor implementations which support both in a configurable manner. While the baseline ISA does not allow for switching between processor endianness, the big-endian order is still useful when supporting big-endian hardware.

Unfortunately, there is no finalized RISC-V specification for bit manipulation. Implementing an endian swap currently requires manually performing swaps on individual bytes. Snippet 4 shows the 64-bit endianness swap for RISC-V without bit manipulation instruction support. Bit manipulation instructions will be introduced with the *B-extension* to the RISC-V ISA.

```

static __inline __uint64_t

__swap64md(__uint64_t _x)

{

__uint64_t ret;

ret = (_x >> 56);

ret |= ((_x >> 40) & 0xff00);

ret |= ((_x >> 24) & 0xff00000);

ret |= ((_x >> 8) & 0xff000000);

ret |= ((_x << 8) & ((__uint64_t)0xff << 32));

ret |= ((_x << 40) & ((__uint64_t)0xff << 40));

ret |= ((_x << 56);

return (ret);

}</pre>

```

Snippet 4. 64-bit endianness swap for RISC-V without bit manipulation instructions.

#### 5.2.4 Trap Frames (frame.h)

The Trap Frames header defines various trap frames used by the kernel when switching between execution contexts. These structures closely mimic the set of registers defined by the RISC-V ISA. When an exception or signal occurs, the trap frame is pushed onto the stack and all of the registers for the active process are saved. This allows for the execution state of a process to be restored once control is handed back by the kernel.

The 64-bit RISC-V ISA defines 32 distinct 64-bit wide integer registers. In the trap frame shown in Snippet 5, space is allocated for 31 of the 32 registers as the x0 register

is hard coded to value 0 and does not need to be saved. In addition to registers, the trap frame also includes a small number of CSRs which are useful during exception handling.

```

* Exception/Trap Stack Frame

*/

#define clockframe trapframe

typedef struct trapframe {

/* Standard Registers */

register_t tf_ra;

register_t tf_sp;

register_t tf_qp;

register_t tf_tp;

register_t tf_t[7];

register_t tf_s[12];

register_t tf_a[8];

/* Supervisor Trap CSRs */

register_t tf_sepc;

register_t tf_sstatus;

register_t tf_stval;

register_t tf_scause;

} trapframe_t;

```

Snippet 5. Trap frame structure.

### 5.2.5 RISC-V Registers (riscvreg.h)

The RISC-V Registers header enumerates constants and functions useful for dealing with RISC-V CSRs. It contains definitions for a number of RISC-V CSRs including the sstatus CSR, which exposes information about the processor state.

### 5.2.6 Process Control Block (pcb.h)

The PCB header defines the process control block structure used by the kernel for process management. It is closely related to context switch. It holds process state such as the state of CPU registers at the time when a process was switched out of a HART. As context switching is normally triggered by a trap, the PCB data structure *struct pcb* in Snippet 6 contains a trap frame to hold the process state saved during trap to the kernel.

# **5.3 Early Bootstrap Implementation**

Section 4.2 describes how the first two bootstrap stages prepare the system for the OS kernel. This section continues describing the kernel bootstrap logic as implemented in

```

struct pcb {

#define PCB_FPU 0v00000001

0x00000001

/* Process had FPU initialized */

#define PCB_SINGLESTEP 0x0000002

/* Single step process */

struct

trapframe *pcb_tf;

register_t

pcb_sp;

// stack pointer of switchframe

pcb_onfault;

caddr_t

// On fault handler

struct fpreg

pcb_fpstate;

// Floating Point state */

struct cpu_info *pcb_fpcpu;

void

*pcb_tcb;

};

```

Snippet 6. Process control block structure.

*locore.S.* Specifically, this section only covers the booting process from the first kernel instruction until the jump to initriscv(), the machine-dependent kernel initialization routine.

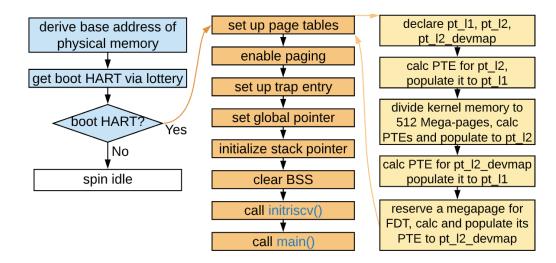

The OpenBSD kernel runs in supervisor-mode. The control flow of *locore.S* is summarized in Figure 17.

Fig. 17. OpenBSD early bootstrap control flow on RISC-V.

### 5.3.1 Starting State

When the OpenBSD kernel boots, it expects the system to be in the following state:

- 1) Register a0 contains a unique HART identifier.

- 2) Register a1 contains a pointer to the FDT.

- 3) System memory is identity-mapped.

- 4) The OS Kernel ELF image is loaded into system memory.

#### 5.3.2 Resolve Kernel Physical Base Address

The kernel physical base address is resolved with the help of virt\_map, which is a quad-word that stores virt\_map's virtual address. This virtual address is specified at link time. By subtracting virt\_map's physical address from its virtual address, an offset is calculated. This offset can be used to resolve a physical address from a virtual address which falls in the kernel virtual address space. The offset is applied to KERNBASE, the kernel virtual base address, to resolve the physical base address of kernel, which is stored in register s9 for further reference.

#### 5.3.3 Determine Boot HART

The OpenBSD kernel expects a single HART to boot the kernel. However, RISC-V HARTs enter the kernel in an arbitrary order from BBL. To handle this impedance mismatch, a very short Atomic Memory Operation (AMO) sequence is executed to select a boot HART. All HARTs attempt to atomically swap a '1' into a location in memory. The HART which successfully swaps its '1' into this memory address, stealing the '0' value held in this location, wins the HART lottery and is chosen to boot the OpenBSD kernel. All other HARTs wait until the boot HART signals that the kernel is ready for multi-processor entry.

### 5.3.4 Set up Page Table

During kernel compile, regions within the .data section are reserved for the initial L1 page table, L2 page table, and L2 device map page table. The kernel builds the initial page tables in these pre-allocated regions of memory. Page Table Entries (PTEs) are

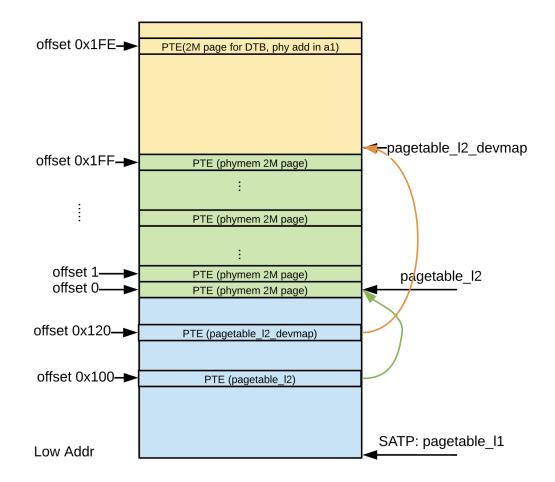

calculated and inserted into these page tables to map the kernel image and FDT into the kernel virtual address space. The detailed procedure for this is shown in the right-most column of Figure 17. The resultant page table structure is shown in Figure 18.

Fig. 18. The initial page table at bootstrap stage.

Once the initial kernel page tables are constructed, a Physical Page Number (PPN) is calculated from the physical address of pagetable\_11. The PPN is combined with the Sv39 virtual address translation mode identifier and written to the supervisor address translation and protection (satp) register to enable paging.

#### 5.3.5 Set up Supervisor Trap Vector

The supervisor trap handler is configured by writing the address of cpu\_trap\_handler to the stvec CSR. This function serves as the entry point into the kernel for all interrupts and exceptions. Interrupt and exception handling is described in Section 5.5.

#### 5.3.6 Jump to C Routine

The kernel prepares for entry into the C runtime:

- 1) Set up Global Pointer gp.

- 2) Set up Stack Pointer sp.

- 3) Clear BSS.

- 4) Fill boot parameters to stack.

Once the C runtime is ready, the boot HART enters into initriscv() which performs more machine-dependent initialization. Afterwards, the entry into main() triggers machine-independent kernel initialization. Later, in the machine-independent kernel initialization, all other HARTs are configured via init\_secondary().

#### 5.4 Memory Subsystem Implementation

OpenBSD relies on the UVM virtual memory system to manage memory resources. The UVM system consists of two layers: a machine-dependent layer and a machine-independent layer. The machine-independent layer is the larger of these two and is shared across all supported architectures. It exposes memory resources at a higher level abstraction over the memory scheme provided by the underlying hardware. The MI layer manages memory of the underlying hardware indirectly through the machine-dependent layer known as the physical map (PMAP). The PMAP layer understands the virtual memory scheme provided by a specific target architecture and acts on requests from the MI layer to map virtual memory addresses to physical memory addresses. Supporting the RISC-V ISA within the OpenBSD memory subsystem involves adapting the PMAP layer to build and modify in-memory page table structures to control the virtual memory layout exposed by RISC-V MMU. This section provides a deep dive into the machine-dependent aspects of managing the RISC-V MMU. It includes both initial MMU configuration early in kernel boot as well as the adaptation of the PMAP layer to manage in-memory page table structures.

#### 5.4.1 Bootstrapping the MMU

The default memory address translation scheme at system boot is Bare which provides a simple identity mapping between virtual and physical memory addresses. In this mode, the virtual memory address 0x8000000 maps to the physical memory address 0x80000000. The other supported memory address translation modes are 4 KiB page-based virtual addressing schemes. Sv39 and Sv48 differ in the number of addressable bits in their virtual address space. Sv39 mode has 39 addressable bits and Sv48 has 48 addressable bits.